Temperature Cycling Chambers in Semiconductor Testing

Temperature cycling chambers serve as indispensable tools in semiconductor manufacturing, enabling engineers to evaluate chip reliability under extreme thermal stress conditions. These specialized test environments replicate real-world temperature fluctuations that electronic components encounter throughout their operational lifespan. By subjecting semiconductor devices to controlled heating and cooling cycles, manufacturers identify potential weaknesses in materials, solder joints, and packaging structures before products reach end users. This preemptive quality assurance approach reduces field failures, extends device longevity, and ensures compliance with stringent industry standards across automotive, aerospace, and consumer electronics sectors.

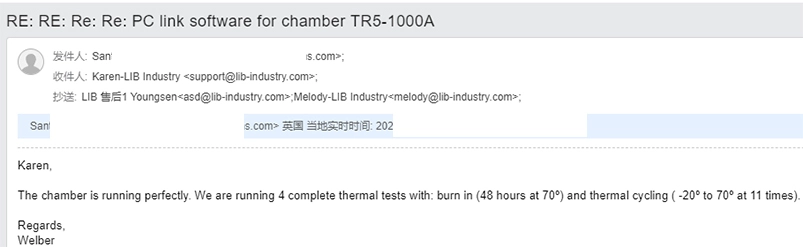

Clients have noted the chambers’ exceptional reliability in practical applications. For instance, a UK-based energy research team successfully conducted multiple comprehensive thermal tests, including extended burn-in cycles and repeated temperature swings, with consistent performance throughout. Their experience highlights the chamber’s robustness and precision, reinforcing its value in high-stakes engineering environments where accuracy and stability are critical.

How Thermal Cycling Impacts Semiconductor Devices

Coefficient of Thermal Expansion Mismatch

Different materials within semiconductor packages expand and contract at varying rates when exposed to temperature changes. Silicon chips, copper interconnects, solder bumps, and epoxy molding compounds each possess unique thermal expansion coefficients. This fundamental material property creates mechanical stress at interfaces during heating and cooling transitions. The accumulated strain from repeated thermal cycles gradually weakens bonding structures, potentially compromising electrical connections and device functionality over time.

Thermomechanical Stress Generation

Rapid temperature transitions induce significant mechanical forces throughout semiconductor assemblies. The temperature cycling chamber generates these stress conditions by alternating between hot and cold extremes at controlled rates. Internal components experience tensile and compressive forces as adjacent materials attempt to expand or contract at different speeds. Critical stress concentration points develop at corners, edges, and material boundaries where geometric discontinuities amplify mechanical loads beyond normal operational levels.

Material Degradation Mechanisms

Prolonged exposure to thermal cycling accelerates various material degradation processes within semiconductor devices. Polymer-based materials undergo glass transition changes that alter mechanical properties and dimensional stability. Metallic layers experience grain boundary migration and intermetallic compound formation at elevated temperatures. These microstructural transformations progressively weaken material integrity, reducing the device's ability to withstand subsequent thermal and electrical stresses during field operation.

Typical Semiconductor Failure Modes Induced by Temperature Cycling

Solder Joint Cracking

Solder interconnections represent the most vulnerable elements in semiconductor packages subjected to thermal cycling. The repetitive expansion and contraction cycles impose low-cycle fatigue conditions on these tiny metallic joints. Microscopic cracks initiate at stress concentration points and propagate through the solder material with each subsequent cycle. Complete electrical discontinuity occurs when cracks traverse the entire joint cross-section, rendering the component non-functional and requiring replacement.

Delamination at Material Interfaces

Adhesive bonds between dissimilar materials weaken under thermal cycling conditions due to differential thermal expansion. The temp cycle chamber exposes these vulnerable interfaces to mechanical peeling forces that exceed adhesive strength limits. Delamination typically initiates at package edges where stress concentrations are highest. Progressive separation creates moisture ingress pathways and thermal resistance barriers that further accelerate device degradation through secondary failure mechanisms.

Wire Bond Failures

Fine metallic wires connecting silicon dies to package leads experience significant thermomechanical stress during temperature cycling. These delicate connections can suffer from bond heel cracking where the wire attaches to metallization pads. Intermetallic compound growth at elevated temperatures creates brittle zones susceptible to fracture. Temperature cycling chambers identify these vulnerabilities by subjecting wire bonds to accelerated aging conditions that simulate years of field operation in compressed timeframes.

Test Parameters for Evaluating Chip and Package Reliability

Test Parameter | Typical Range | Significance |

Temperature Range | -40°C to +150°C | Simulates operating environment extremes |

Ramp Rate | 5-15°C/min | Controls stress application speed |

Dwell Time | 10-30 minutes | Ensures thermal equilibrium at extremes |

Cycle Count | 100-1000 cycles | Determines cumulative damage threshold |

Chamber Volume | 100-1000L | Accommodates various sample quantities |

Temperature Extremes Selection

Engineers select temperature range limits based on anticipated application environments and industry specifications. Automotive semiconductor testing typically employs -40°C to +150°C ranges reflecting under-hood conditions and extreme climates. Consumer electronics applications may utilize narrower ranges between -20°C and +85°C corresponding to normal usage scenarios. The temperature cycling chamber must achieve stable control across the entire specified range to ensure reproducible test conditions.

Transition Rate Configuration

The speed at which temperature changes occur significantly influences the stress magnitude imposed on semiconductor devices. Higher ramp rates generate steeper thermal gradients within package structures, creating more severe mechanical stress conditions. Controllable heating and cooling rates between 5°C and 15°C per minute allow engineers to tailor test severity levels. Linear temperature transitions ensure predictable thermal stress application rather than unpredictable fluctuations that complicate data interpretation.

Cycle Duration Optimization

Each thermal cycle consists of heating, hot dwell, cooling, and cold dwell segments that collectively determine total test duration. Adequate dwell periods at temperature extremes enable complete thermal saturation throughout device structures, ensuring uniform stress exposure. Insufficient dwell times create temperature gradients within samples that produce non-representative test results. Programmable controllers in modern temperature cycling chambers automatically execute complex cycle profiles with precise timing control.

Accelerated Aging and Lifetime Prediction for Semiconductors

Arrhenius Relationship Application

The Arrhenius equation provides the mathematical foundation for accelerating failure mechanisms through elevated stress conditions. This relationship quantifies how reaction rates double approximately every 10°C temperature increase, enabling compressed lifetime testing. Temperature cycling chambers operating at elevated stress levels accumulate damage equivalent to years of normal operation within weeks or months. Engineers calculate acceleration factors to extrapolate chamber test results into field lifetime predictions with statistical confidence.

Coffin-Manson Fatigue Model

Low-cycle fatigue failures in solder joints and interconnects follow the Coffin-Manson relationship between temperature range and cycles to failure. This empirical model enables engineers to predict service life based on operational temperature swing magnitude. The temperature cycling test chamber generates controlled thermal excursions with precise amplitude regulation essential for Coffin-Manson parameter determination. Material constants derived from chamber testing inform reliability predictions across different application temperature profiles.

Weibull Distribution Analysis

Failure time data from temperature cycling chamber tests typically follows Weibull statistical distributions rather than normal Gaussian patterns. This distribution model accommodates the characteristic infant mortality, random failure, and wear-out phases observed in semiconductor reliability. Engineers extract Weibull shape and scale parameters from chamber test data to quantify failure rate evolution throughout product lifecycles. These statistical tools transform raw test observations into actionable reliability metrics for design optimization.

Reliability Metric | Calculation Method | Design Application |

MTTF (Mean Time to Failure) | Integration of failure distribution | Warranty period determination |

Characteristic Life (η) | 63.2% failure point on Weibull plot | Comparative reliability assessment |

Shape Parameter (β) | Slope of Weibull distribution | Failure mechanism identification |

Data Analysis and Reporting in Semiconductor Thermal Tests

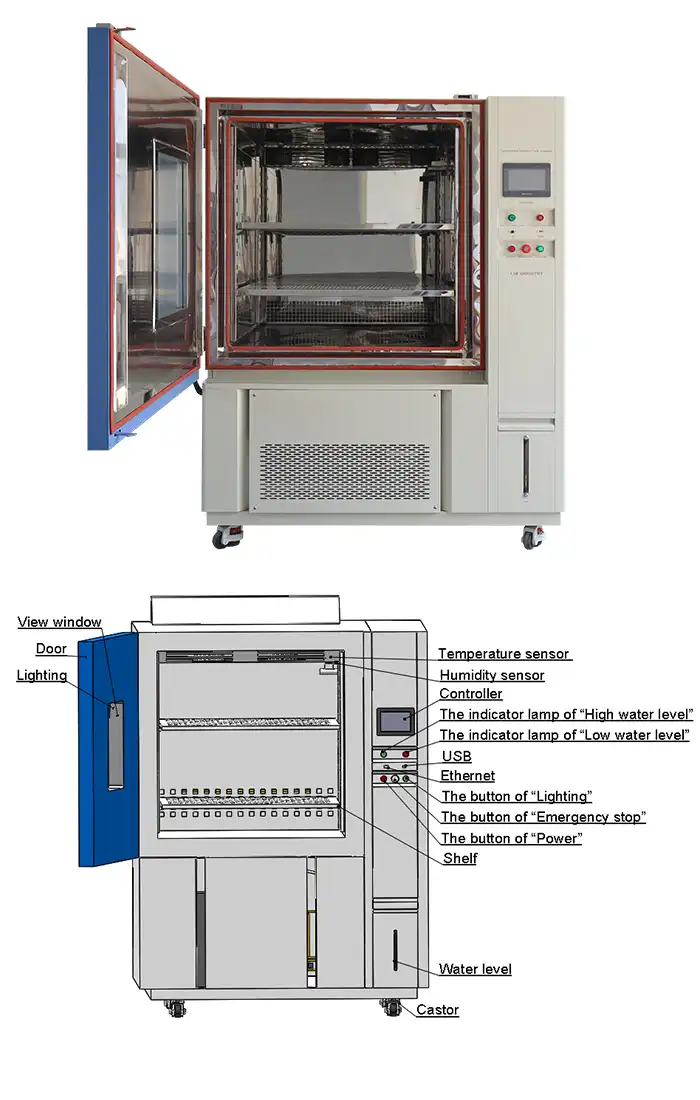

Real-Time Monitoring Capabilities

Modern temperature cycling chambers incorporate sophisticated data acquisition systems that continuously track chamber conditions and sample responses. High-precision PT100 Class A temperature sensors provide 0.001°C resolution measurements throughout test volumes. Ethernet connectivity enables remote monitoring via mobile applications and web interfaces, allowing engineers to supervise experiments from any location. This continuous oversight ensures immediate detection of anomalous conditions that might compromise test validity.

Automated Data Logging Systems

Comprehensive data storage solutions capture temperature profiles, cycle counts, and timing information throughout extended test campaigns. USB interfaces facilitate periodic data downloads for archival purposes and detailed analysis. FDA 21 CFR Part 11 compliant data management systems provide audit trails necessary for regulated industries like medical devices and aerospace components. This documentation capability ensures complete traceability from raw measurements through final reliability conclusions.

Statistical Process Control Integration

Temperature cycling chamber data feeds directly into broader quality management systems employing statistical process control methodologies. Control charts track key performance indicators like failure rates and cycles to first failure across production lots. Trend analysis identifies gradual reliability degradation patterns that signal process drift requiring corrective action. This integration transforms isolated test data into actionable manufacturing intelligence supporting continuous improvement initiatives.

Enhancing Device Robustness Through Temperature Cycling

Design Validation Methodology

Temperature cycling chambers enable iterative design refinement by exposing prototype weaknesses before production commitment. Engineers evaluate multiple package configurations, material combinations, and assembly processes through comparative thermal cycling tests. Rapid feedback from chamber evaluations guides design modifications that eliminate failure modes systematically. This validation approach compresses development timelines while simultaneously improving final product reliability margins.

Process Optimization Strategies

Manufacturing process variables significantly influence semiconductor device thermal cycling performance. Solder reflow profiles, cure temperatures for adhesives, and wire bonding parameters all contribute to final assembly robustness. The temperature cycling chamber quantifies how process adjustments affect reliability outcomes through designed experiments. Optimized manufacturing windows emerge from these systematic investigations, balancing cost efficiency with quality requirements.

Supplier Qualification Programs

Component suppliers must demonstrate thermal cycling compliance before qualification for production use. Standardized chamber test protocols establish objective performance benchmarks that all vendors must achieve. Comparative testing across multiple suppliers identifies materials and processes offering superior reliability characteristics. This data-driven supplier selection process minimizes supply chain risks while maintaining competitive sourcing options.

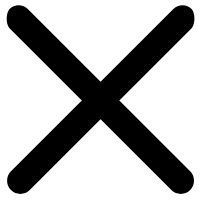

High-Precision Stress Screening with LIB Industry Temperature Cycling Chambers

Advanced Refrigeration Architecture

LIB Industry temperature cycling chambers employ multi-stage cascade refrigeration systems featuring premium Bitzer compressors for reliable operation during intensive cycling protocols. PID control algorithms with automatic refrigerant flow adjustment through electronic expansion valves maintain precise temperature regulation. Advanced anti-frost technology preserves system efficiency during extended test campaigns at extreme low temperatures. This sophisticated thermal management enables linear heating and cooling rates rather than averaged values that obscure true performance capabilities.

Comprehensive Safety Infrastructure

Dual-layer protection systems combine independent hardware temperature limiters with software controls preventing runaway conditions. Smoke detection and fire suppression system integration provides additional safeguards for lithium battery testing applications. Pressure relief valves automatically adjust internal pressure during rapid temperature transitions, protecting both samples and chamber integrity. Electrical leakage protection, grounding security, and phase monitoring create a comprehensive safety envelope around test operations.

Customization and Support Capabilities

Feature Category | Standard Offering | Customization Options |

Chamber Volume | 100L to 1000L | Modified dimensions for specific samples |

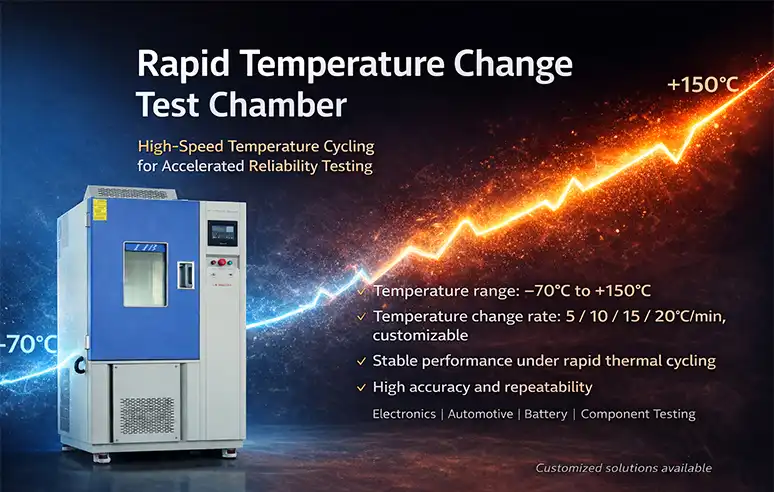

Temperature Range | -70°C to +150°C | Extended ranges for specialized applications |

Sample Fixtures | 2 shelves included | Application-specific holders and supports |

System Integration | Ethernet PC Link | Laboratory information management connectivity |

LIB Industry maintains ISO 9001 Quality Management System certification alongside CE compliance verified through independent SGS and TUV testing. Global partnerships with technology leaders demonstrate the reliability and performance of these thermal cycling solutions. International service centers in Malaysia, Canada, the UK, and the US provide comprehensive support ensuring minimal operational downtime. Every unit includes a 3-year warranty with lifetime service support backed by 24/7 technical assistance availability.

| Name | Temperature Cycling Chamber | ||||

Model | TH-100 | |||||

Temperature range | -20℃ ~+150 ℃ | |||||

Low type | A: -40℃ B:-70℃ C -86℃ | |||||

Humidity Range | 20%-98%RH | |||||

Temperature deviation | ± 2.0 ℃ | |||||

Heating rate | 3 ℃ / min | |||||

Cooling rate | 1 ℃ / min | |||||

Controller | Programmable color LCD touch screen controller, Multi-language interface, Ethernet , USB | |||||

Exterior material | Steel Plate with protective coating | |||||

Interior material | SUS304 stainless steel | |||||

Standard configuration | 1 Cable hole (Φ 50) with plug; 2 shelves | |||||

Timing Function | 0.1~999.9 (S,M,H) settable | |||||

Conclusion

Temperature cycling chambers constitute essential infrastructure for semiconductor reliability engineering, enabling manufacturers to validate device robustness before market introduction. These sophisticated test systems replicate years of thermal stress exposure within compressed timeframes, revealing potential failure modes that might otherwise escape detection until field deployment. The integration of precision control systems, comprehensive data acquisition, and advanced refrigeration technology empowers engineers to make informed decisions regarding design optimization, process refinement, and supplier qualification. Investing in high-quality thermal cycling capabilities represents a strategic commitment to product excellence and customer satisfaction.

FAQ

What distinguishes temperature cycling from thermal shock testing in semiconductor applications?

Temperature cycling employs controlled ramp rates between temperature extremes with defined dwell periods, simulating gradual environmental changes. Thermal shock testing uses extremely rapid transitions, often through physical transfer between hot and cold zones, generating more severe stress conditions that accelerate specific failure mechanisms like brittle fracture.

How many thermal cycles should semiconductor packages undergo during qualification testing?

Industry standards typically specify between 500 and 1000 cycles for production qualification testing, though specific requirements vary by application sector. Automotive applications often demand higher cycle counts reflecting harsh operating environments, while consumer electronics may utilize fewer cycles based on expected usage patterns and warranty obligations.

Can temperature cycling chambers accommodate functional testing of powered semiconductor devices?

Modern chambers incorporate cable ports with silicone seals enabling electrical connections to devices under test. This configuration allows simultaneous thermal cycling and functional parameter monitoring, revealing performance degradation trends before catastrophic failures occur. Real-time electrical characterization provides insights into gradual degradation mechanisms complementing traditional failure analysis approaches.

Contact LIB Industry for Your Testing Solutions

As a leading temperature cycling chamber manufacturer and supplier, LIB Industry provides comprehensive environmental testing solutions tailored to semiconductor applications. Our engineering team develops customized configurations meeting your unique reliability requirements. Contact us at ellen@lib-industry.com to discuss how our thermal cycling chambers can strengthen your quality assurance programs.